SUPPORT TECHNIQUE

**NOTICE

TECHNIQUE

CARTE**

**CPU 68B09**

N° 6701100

SMT/GOUPIL

SUPPORT TECHNIQUE

S U M M A R Y

I/ Présentation

II/ Le MC 68 B 09

A) Présentation

B) Description des Signaux

**N O T I C E**

... registres du 68 B 09

**T E C H N I Q U E**

III/ C A R T E Atteur d'adresses

A) Description

B) Fonction

**C P U    6 8 B Ø 9**

IV/ Le Moniteur Dynamique

V/ Les Entrées-Sorties

A) Description du 68 B 50

B) Le BRG 1941

VI/ Le Moniteur

VII/ Circuits Divers

VIII/ Annexe

SMT/GOUPIL

CODE S.M.T. 6701100

S O M M A I R E

---

- I/ Présentation

- II/ Le MC 68 B 09

- A) Présentation

- B) Description des Signaux

- C) Les registres du 68 B 09

- D) Chronogrammes

- III/ Le Translateur d'adresses

- A) Description

- B) Utilisation

- IV/ La mémoire dynamique

- V/ Les Entrées-Sorties

- A) Description du 68 B 50

- B) Le BRG 1941

- VI/ Le Moniteur

- VII/ Circuits Divers

- VIII/ Annexe

-o-o-o-o-o-o-o-o-o-o-o-

## I- Présentation

- La carte CPU 68B09 version 1 du Goupil 3 est une des trois cartes micro-processeur disponible sur ce micro-ordinateur. Elle est architecturée autour du microprocesseur 68B09 de Motorola, circuit intégré VLSI qui constitue une amélioration sensible du MC 6800. Le Goupil 2 utilise une des versions du MC 6800, le MC 6808. L'utilisation du MC 68B09 permet de disposer à la fois d'une plus grande puissance et d'une plus grande souplesse de programmation. L'ensemble de ses particularités matérielles et logiciels font du 68B09 l'un des meilleurs microprocesseur 8 bits du marché.

- La carte CPU inclue également 64 kilo-octets de mémoire dynamique, les circuits nécessaires à l'adressage de 1 méga-octet de mémoire et deux entrées sorties séries dont une disponible pour l'utilisateur. Le moniteur de base du Goupil 3 est également implanté sur cette carte (en partie seulement pour la version 1).

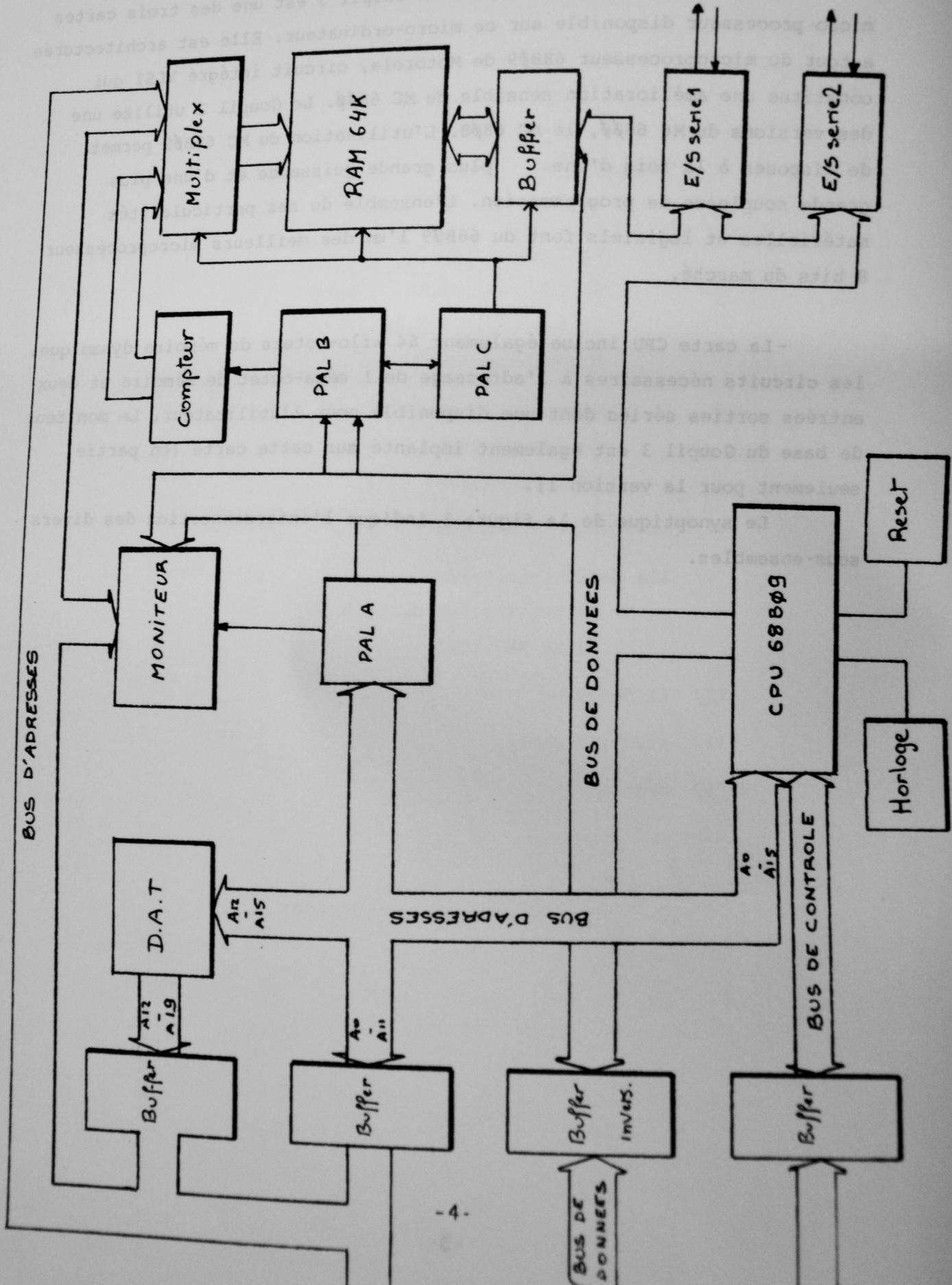

Le synoptique de la figure 1 indique l'interconnection des divers sous-ensembles.

+ synoptique +

## II- Le MC 68B09

### A) Présentation

C'est un microprocesseur 8 bits dont les principales caractéristiques sont résumées ci-après :

- compatible au niveau matériel (périphérique) et logiciel avec le 6800,

- quatre registres internes de 16 bits,

- deux accumulateurs de 8 bits pouvant former un accumulateur de 16 bits,

- un registre de page direct permettant de faire de l'adresse direct sur toute la mémoire,

- 10 modes d'adressage englobant ceux du 6800,

- multiplication 8x8 non signée,

- transfert et échange de tous les registres,

- instruction "chargement de l'adresse effective",

- oscillateur incorporé,

- entrée DMA/BREQ permettant l'accès DMA,

- interruption rapide FIRQ.

### B) Description des signaux

VSS      borne 1      OV

VCC      borne 7      SV 15%

Ao-A15      borne 8-23      16 lignes d'adresses valides sur le front montant de Q. Lorsque le MPU ne fait pas d'accès mémoire il positionne ces lignes à FFFF avec R/W = 1 et BS = 0. Les lignes d'adresses sont mises à haute impédance lorsque le signal BA (Bus Available) est au niveau logique haut.

Do D7      borne 24-31      8 lignes de données.

FIGURE 2

+ BROCHAGE DU 6809 +

A) BRÈVE DESCRIPTION

|    |      |          |    |

|----|------|----------|----|

| 1  | VSS  | HALT     | 40 |

| 2  | NMI  | XTAL     | 39 |

| 3  | IRQ  | EXTAL    | 38 |

| 4  | FIRQ | RESET    | 37 |

| 5  | BS   | MRDY     | 36 |

| 6  | BA   | Q        | 35 |

| 7  | VCC  | E        | 34 |

| 8  | A0   | DMA/BREQ | 33 |

| 9  | A1   | R/W      | 32 |

| 10 | A2   | DO       | 31 |

| 11 | A3   | DI       | 30 |

| 12 | A4   | D2       | 29 |

| 13 | A5   | D3       | 28 |

| 14 | A6   | D4       | 27 |

| 15 | A7   | D5       | 26 |

| 16 | A8   | D6       | 25 |

| 17 | A9   | D7       | 24 |

| 18 | A10  | A15      | 23 |

| 19 | A11  | A14      | 22 |

| 20 | A12  | AB       | 21 |

R/W borne 32 R/W = 1 le MPU fait une lecture - R/W = 0 le MPU fait une écriture validé sur le front de Q.

Reset borne 37 un niveau bas sur cette entrée pendant plus d'un cycle d'horloge "reset" le MPU. Le vecteur reset est chargé en mémoire aux adresses FFFE et FFFF lorsque BS = 1.

Halt borne 40 un niveau bas sur cette ligne stoppera le MPU à la fin de la présente instruction. Le MPU positionne la ligne BA à 5V pour indiquer que ses lignes sont à haute impédance. Pendant qu'il est arrêté le MPU ne répond pas à la demande d'interruption (FIRQ et IRQ). NMI et Reset sont latchés pour réponse ultérieure.

BA, BS 6,5 BA (Bus disponible) indique que le MPU est arrêté et que ses lignes de bus sont à haute impédance. BS (Bus status) indique l'état du MPU.

| BA | BS |                               |

|----|----|-------------------------------|

| 0  | 0  | normal                        |

| 0  | 1  | reconnaissance d'interruption |

| 1  | 0  | reconnaissance de SYNC        |

| 1  | 1  | halt ou Bus Grant             |

NMI borne 2 un front descendant sur cette entrée génère une interruption non masquable prioritaire. Après reconnaissance de NMI l'ensemble des registres du MPU est sauvegardé dans la pile. Après un Reset, un NMI ne peut être reconnue tant que le registre de pointeur de pile S n'a pas été chargé.

FIRQ borne 4 demande d'interruption rapide. Un niveau bas initialise une séquence d'interruption rapide si le bit F du registre d'état du 6809 n'est pas positionné. Seuls PC et CC sont sauvegardés dans la pile.

IRQ borne 3 demande d'interruption. Si le bit I de CC n'est pas positionné, l'ensemble des registres est sauvegardé dans la pile.

Table des vecteurs d'interruption

|      |      |              |

|------|------|--------------|

| FFFE | FFFF | <u>Reset</u> |

| FFFC | FFFD | <u>NMI</u>   |

| FFFA | FFFB | <u>SWI</u>   |

| FFF8 | FFF9 | <u>IRQ</u>   |

| FFF6 | FFF7 | <u>FIRQ</u>  |

| FFF4 | FFF5 | <u>SWI2</u>  |

| FFF2 | FFF3 | <u>SWI3</u>  |

XTAL, EXTAL 39-38 Connection d'un quartz pour générer l'horloge système

L'entrée EXTAL peut recevoir une horloge égale à 8x l'horloge système ; il faut alors relier la borne 38 au OV.

E, Q 34-35 E et Q sont 2 horloges générées par le 6809. Le début d'un cycle MPU commence sur le front descendant de E. Q. et en quadrature avec E.

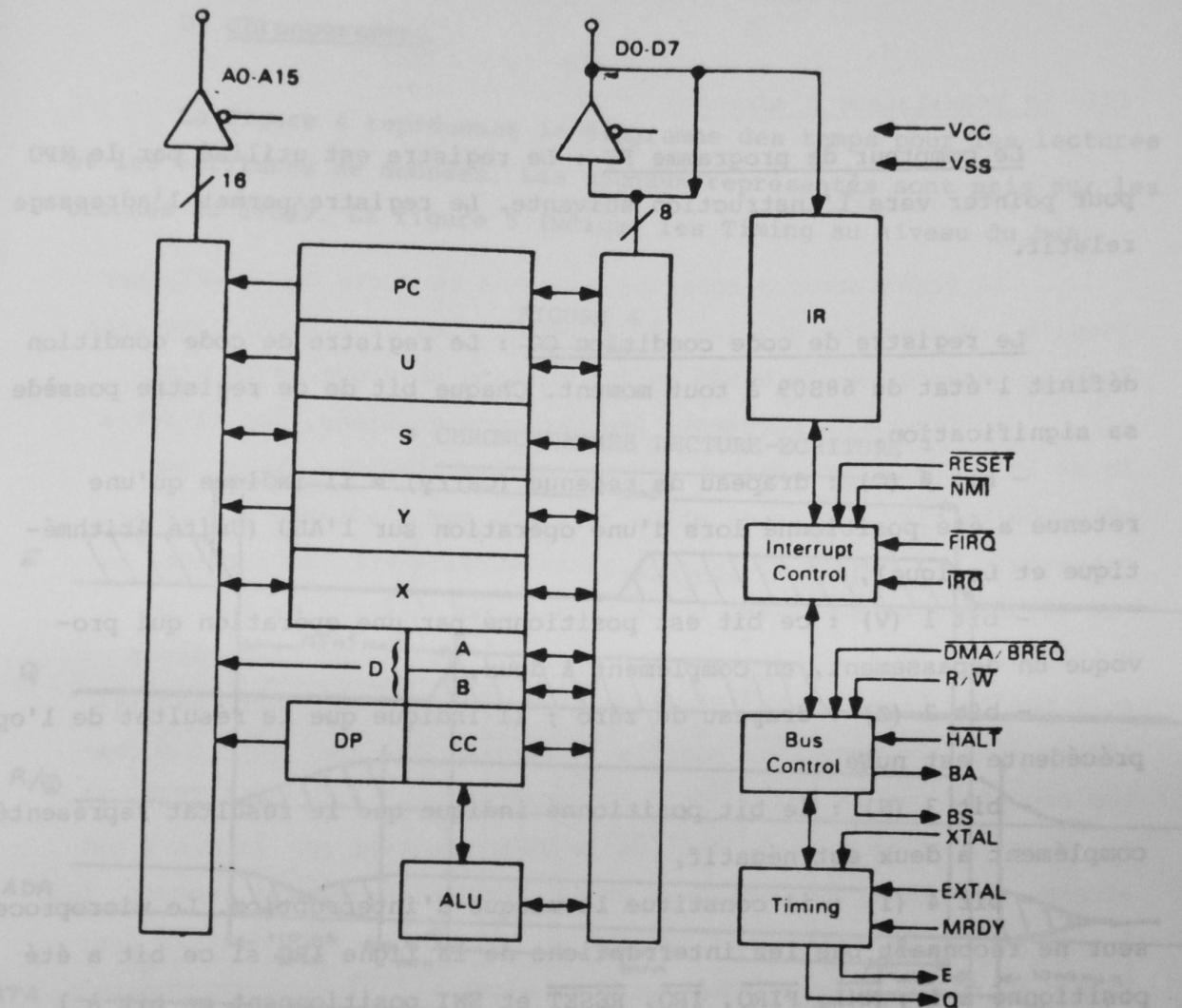

FIGURE 3 - MC6808 EXPANDED BLOCK DIAGRAM

MRDY 36

DMA/BREQ 33

lorsque MRDY est à OV, E est maintenu à l'état haut et Q à l'état bas pendant des multiples de quart de cycle. Permet l'affichage des mémoires lentes. cette ligne maintenue au niveau bas permet de stopper le MPU à la fin du cycle en cours. Cette ligne est échantillonnée sur le front descendant de E. En réponse le MPU positionne les lignes BA et BS, libérant les bus.

permettre de bus difficile DS : Ce registre sera à nouveau si

mises à disposition. Le contenu de ce registre correspond à l'ocer de

bonds lors fois fois d'un adressé direct qui le fait faire une pause si ne-

mote. L'ordre dépend de la combinaison avec le code de l'émis-

sion de bus. Bus Control BA

y à fois, un Reset :

permettre à l'index X si Y : Les registres sont multipliés dans

le sens d'adressage linéaire. Pas de perte d'adresses de ces registres sous

utilisées pour certains, l'adresse élégante du mémoire. Dans certains

cas, il y a une séparation de ces registres basé sur la hiérarchie de

séquence de l'adressage.

les boucles de bus U et B : la boucle de bus A est

utilisé pour déclencher les MPU demandes d'accès aux bus de l'unité

de l'interprétation. Le registre U est chargé exclusivement par l'unité

pour ce qui concerne les bases de systèmes qui sont brodées

en à la suite. Les registres U et B sont utilisés pour déclencher l'adres-

sage à l'index des registres X et Y.

PC = compteur de programme

U = pointeur de pile

S = pointeur de pile système

Y = registre d'index Y

X = registre d'index X

A,B = accumulateur à bit D = A + B

DP = registre de page

ALU = Unité arithmétique et logique

### C) Les registres du 68B09

Le 68B09 possède 9 registres internes : 4 registres 8 bits et 5 registres de 16 bits. La figure 3 représente le "block diagram".

Les accumulateurs A et B : Ces 2 registres sont comparables à ceux du MC 6800. Ce sont des registres d'usage général par lesquels se font les transferts de données et les calculs. Certaines instructions utilisent le registre D formé de A et de B, A étant l'octet de poids fort.

Le registre de page directe DP : Ce registre sert à augmenter le mode d'adressage direct. Le contenu de ce registre constitue l'octet de poids fort lors d'un adressage direct qui se fait alors sur toute la mémoire. Pour garder la compatibilité avec le 6800, ce registre est remis à 0 lors du Reset.

Les registres d'index X et Y : Les registres sont utilisés dans le mode d'adressage indexé. Les 16 bits d'adresse de ces registres sont utilisés pour calculer l'adresse effective en mémoire. Dans certains modes d'adressage le contenu de ces registres peut être incrémenté ou décrémenté automatiquement.

Les pointeurs de pile U et S : Le pointeur de pile système S est utilisé automatiquement par le MPU pendant l'appel de sous-programme et les interruptions. Le registre U est contrôlé exclusivement par l'utilisateur ce qui permet des passages faciles de paramètres d'un sous programme à un autre. Les registres U et S supportent également l'adressage indexé des registres X et Y.

FIGURE 3 – MC6809 EXPANDED BLOCK DIAGRAM

PC = compteur de programme

U = pointeur de pile

S = pointeur de pile système

Y = registre d'index Y

X = registre d'index X

A.B = accumulateur 8 bit D = A + B

DP = registre de page

ALU = unité arithmétique et logique

Le compteur de programme PC : Le registre est utilisé par le MPU pour pointer vers l'instruction suivante. Le registre permet l'adressage relatif.

Le registre de code condition CC : Le registre de code condition définit l'état du 68B09 à tout moment. Chaque bit de ce registre possède sa signification.

- bit 0 (C) : drapeau de retenue (carry) = il indique qu'une retenue a été positionné lors d'une opération sur l'ALU (Unité Arithmétique et Logique),

- bit 1 (V) : ce bit est positionné par une opération qui provoque un dépassement, en complément à deux,

- bit 2 (Z) : drapeau de zéro ; il indique que le résultat de l'opération précédente est nulle,

- bit 3 (N) : le bit positionné indique que le résultat représenté en complément à deux est négatif,

- bit 4 (I) : il constitue le masque d'interruption. Le microprocesseur ne reconnaît pas les interruptions de la ligne IRQ si ce bit a été positionné à 1 ; NMI, FIRQ, IRQ, RESET et SWI positionnent ce bit à 1 tandis que SWI2 et SWI3 ne le positionnent pas.

- bit 5 (H) : ce bit est la demi-retenue du bit 3 dans les opérations d'addition sur 8 bits,

- bit 6 (F) : ce bit masque les interruptions rapides lorsqu'il est positionné,

- bit 7 (E) : ce bit positionné indique que la totalité des registres a été sauvegardée lors de l'appel du sous-programme ou de la routine d'interruption précédent.

FIGURE 5

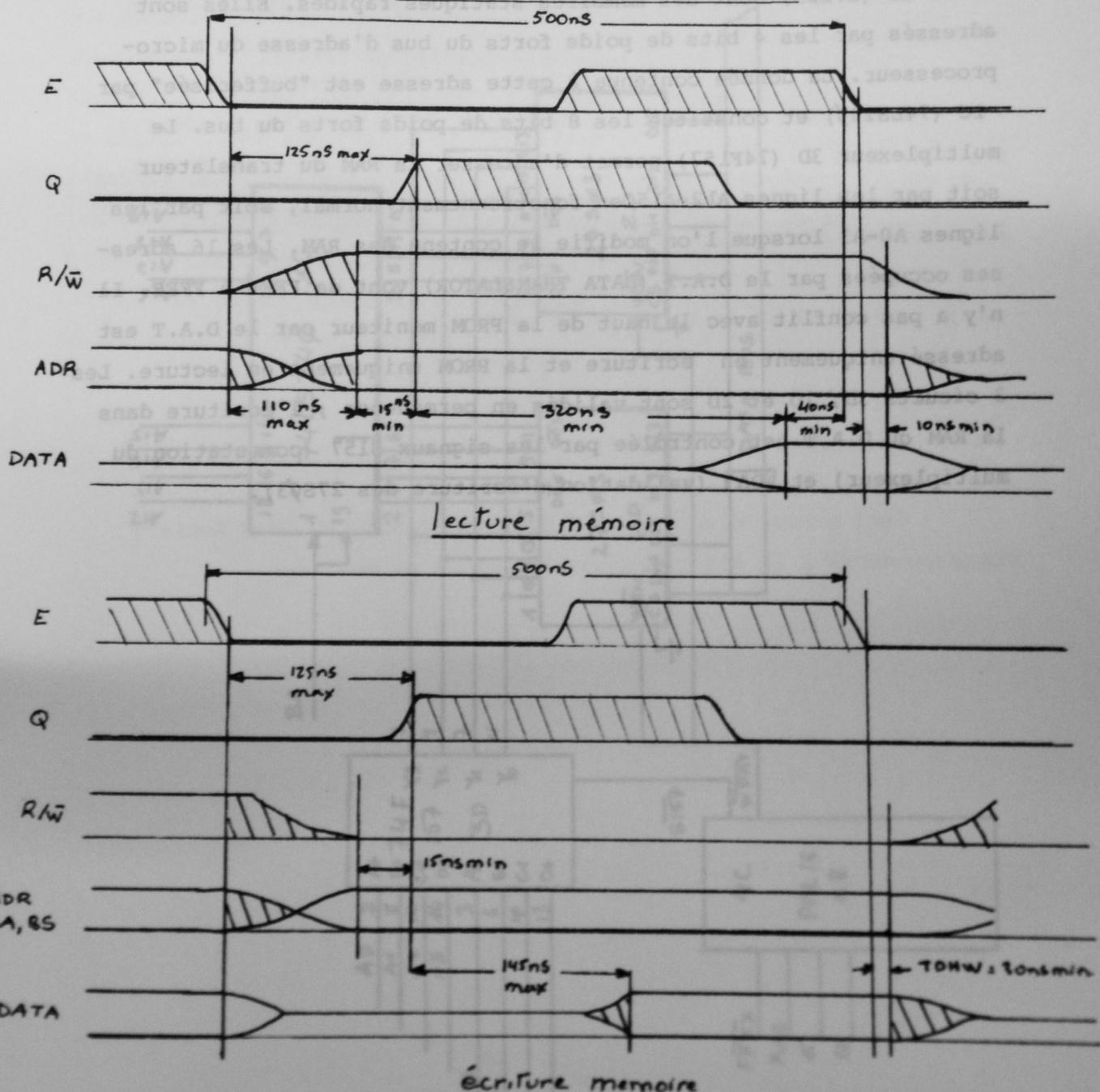

## D) Chronogrammes

La figure 4 représente le diagramme des temps pour les lectures et les écritures de données. Les signaux représentés sont pris sur les broches du 68B09. La figure 5 indique les Timing au niveau du bus.

FIGURE 4

## + CHRONOGRAMMES LECTURE-ÉCRITURE +

### III- Le Translateur d'adresses

#### A) Description

Le translateur d'adresses permet à la carte CPU d'adresser jusqu'à 1 MOctets de mémoire. Il convertit les 16 bits de l'adresse logique générée par le 68B09 en une adresse physique de 20 bits.

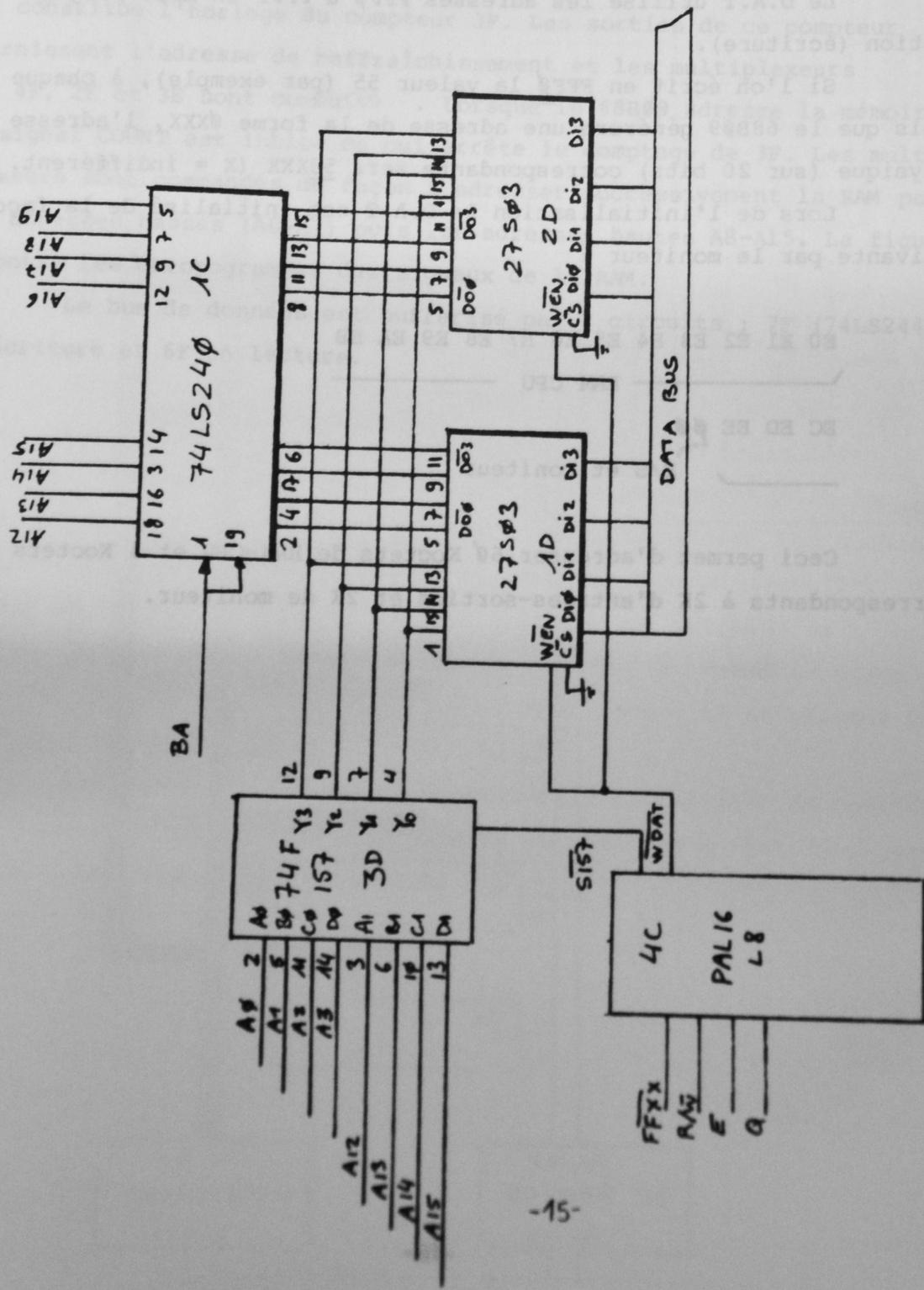

La figure 4 représente les circuits utilisés. Les circuits 1D et 2D (27S03) sont des mémoires statiques rapides. Elles sont adressés par les 4 bits de poids forts du bus d'adresse du micro-processeur. La donnée contenue à cette adresse est "bufferisée" par 1C (74LS240) et constitue les 8 bits de poids forts du bus. Le multiplexeur 3D (74F157) permet d'adresser la RAM du translateur soit par les lignes A12-A15 en fonctionnement normal, soit par les lignes A0-A3 lorsque l'on modifie le contenu des RAM. Les 16 adresses occupées par le D.A.T (DATA TRANSLATOR) vont de FFF0 à FFFF. Il n'y a pas conflit avec le haut de la PROM moniteur car le D.A.T est adressé uniquement en écriture et la PROM uniquement en lecture. Les 3 circuits 3D, 1D et 2D sont validés en permanence ; l'écriture dans la RAM du D.A.T est contrôlée par les signaux S157 (commutation du multiplexeur) et WDAT (validation d'écriture des 27S03).

FIGURE 5

+ TRANSLATEUR D'ADRESSE +

## B) Utilisation

Le translateur d'adresses fournit sur le bus les adresses A12-A19. Les adresses A0-A11 générées par le 68B09 ne sont pas transformées et sont envoyées sur le bus à travers 1B et 2A (74LS244). Il est possible donc sans modifier la programmation du D.A.T d'adresser 16 blocs de 4 K octets. En modifiant le D.A.T il est possible d'obtenir sur A12-A19 256 combinaisons différentes ce qui porte l'adressage à 256 x 4Koctets soit 1 Moctets.

Le D.A.T utilise les adresses FFF0 à FFFF en mode programmation (écriture).

Si l'on écrit en FFF0 la valeur 55 (par exemple), à chaque fois que le 68B09 générera une adresse de la forme 0XXX, l'adresse physique (sur 20 bits) correspondante sera 55XXX (X = indifférent).

Lors de l'initialisation le D.A.T est initialisé de la façon suivante par le moniteur :

E0 E1 E2 E3 E4 E5 E6 E7 E8 E9 EA EB

\_\_\_\_\_ RAM CPU \_\_\_\_\_

EC ED EE

\_\_\_\_\_, E/S et moniteur

Ceci permet d'adresser 60 Koctets de RAM-CPU et 4 Koctets correspondants à 2K d'entrées-sorties et 2K de moniteur.

#### IV- La mémoire dynamique

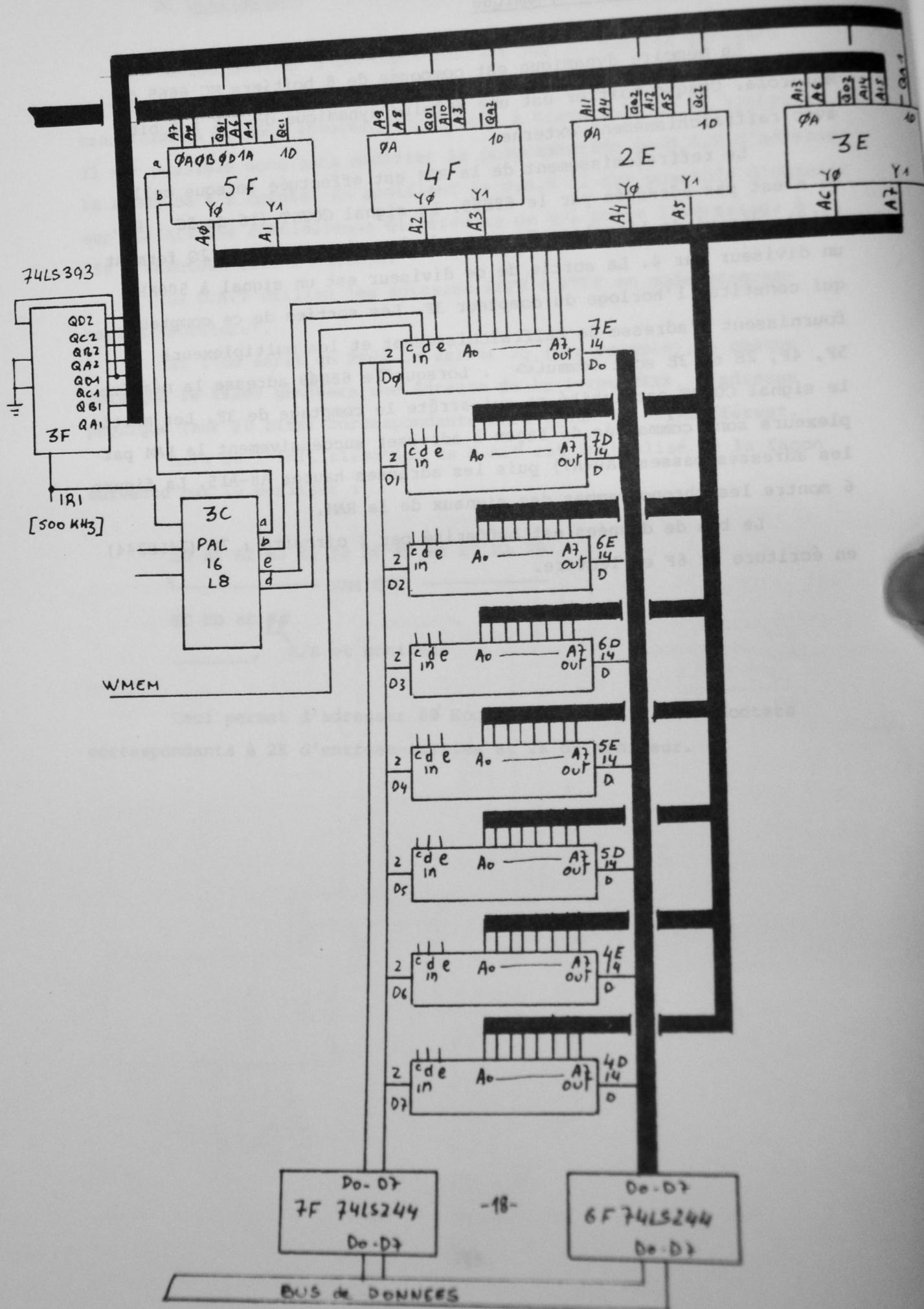

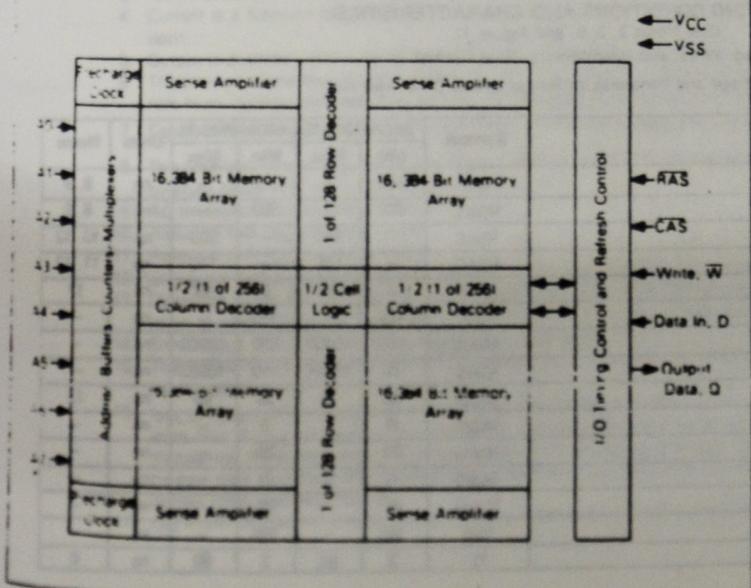

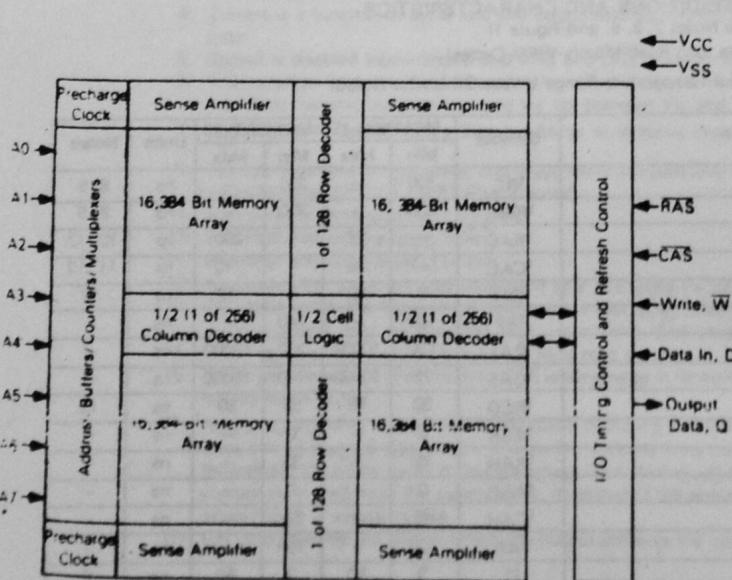

La mémoire dynamique est composée de 8 boitiers MC 6665 de Motorola. Chaque boitier est une mémoire dynamique de 64K x 1 bit avec raffraîchissement externe.

Le raffraîchissement de la RAM est effectuée lorsque celle ci n'est pas adressée par le 68B09. Le signal COUNT (16 de 5C : PAL 16L8), dérivé de l'horloge E, commande les circuits 1G et 2G formant un diviseur par 4. La sortie de ce diviseur est un signal à 500KHz qui constitue l'horloge du compteur 3F. Les sorties de ce compteur fournissent l'adresse de raffraîchissement et les multiplexeurs 5F, 4F, 2E et 3E sont commutés. Lorsque le 68B09 adresse la mémoire, le signal COUNT est inhibé ce qui arrête le comptage de 3F. Les multiplexeurs sont commandés de façon à adresser successivement la RAM par les adresses basses (A0-A7) puis les adresses hautes A8-A15. La figure 6 montre les chronogrammes des signaux de la RAM.

Le bus de données est bufferisé par 2 circuits ; 7F (74LS244) en écriture et 6F en lecture.

## + LA RAM DYNAMIQUE +

## V- Les entrées-sorties séries

La carte CPU 68B09 comporte 2 entrées sorties séries dont une est utilisée par le clavier.

Chaque canal comporte :

- 2 lignes d'échanges RD (Receive Data) et TD (Transmit Data)

- 3 lignes de contrôle d'un MODEM

- RTS (Request To Send) indique au MODEM qu'un caractère est prêt à être transmis.

- CTS (Clear To Send) indique à l'ACIA que le MODEM n'accepte plus de données.

- DCD (Data Carrier Detect). Le MODEM a détecté une porteuse de données.

Dans le cas d'une utilisation sans MODEM, relier CTS et DCD au + 12 V et ne pas connecter RTS.

### A) Description du 6850

L'ACIA 6850 (Asynchronous Communication Interface Adapter) permet une liaison série du type asynchrone telle que celle d'une télétype. Le format des données et la vitesse de transmission sont définis par le système durant la phase d'initialisation. Les données à serialiser sont stockées dans un registre de transmission (TRD) via le bus de données. L'horloge interne (obtenue par division de l'horloge externe TXC) se charge de serialiser la donnée. Les données reçues par la ligne RD sont rangées dans un registre de réception et peuvent être lues par le système.

Deux autres registres sont utilisés : le registre de contrôle (CR) permettant de configurer l'ACIA et le registre d'état (SR) permettant de connaître l'état de l'ACIA.

## DESCRIPTION DES REGISTRES

Registre de transmission (TDR) - RS = 1, R/W = 0

bit 7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

- Le bit 7 n'est pas utilisé dans le cas d'une transmission sur 7 bits.

Registre de réception (RDR) RS = 1 - R/W = 1

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

- Le bit 7 n'est pas utilisé pour une transmission sur 7 bits.

Registre de contrôle (CR) RS = Ø et R/W = Ø

|     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CR7 | CR6 | CR5 | CR4 | CR3 | CR2 | CR1 | CR0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

Choix de l'horloge CR0 - CR1

| CR1 | CRØ | FONCTION                          |

|-----|-----|-----------------------------------|

| Ø   | Ø   | Horloge interne = horloge externe |

| Ø   | 1   | Horloge interne = 1/16 externe    |

| 1   | Ø   | Horloge interne = 1/64 externe    |

| 1   | 1   | Master Reset                      |

- Si CR1 et CRØ sont à 1, on effectue le Master Reset (Reset programmé). A effectuer avant chaque initialisation.

Choix du format de transmission CR 2 - CR 3 CR 4

| CR4 | CR3 | CR2 | FONCTION                              |

|-----|-----|-----|---------------------------------------|

| 0   | 0   | 0   | 7 bits + parité paire + 2 bits stop   |

| 0   | 0   | 1   | 7 bits + parité impaire + 2 bits stop |

| 0   | 1   | 0   | 7 bits + parité paire + 1 bit stop    |

| 0   | 1   | 1   | 7 bits + parité impaire + 1 bit stop  |

| 1   | 0   | 0   | 8 bits + 2 stops                      |

| 1   | 0   | 1   | 8 bits + 1 stop                       |

| 1   | 1   | 0   | 8 bits + parité paire + 1 stop        |

| 1   | 1   | 1   | 8 bits + parité impaire + 1 stop      |

Contrôle de la ligne RTS CR 6 - CR 5

| CR6 | CR5 | FONCTION                                                    |

|-----|-----|-------------------------------------------------------------|

| 0   | 0   | RTS = 0, pas d'interruption en transmission                 |

| 0   | 1   | RTS = 0, interruption validée en transmission               |

| 1   | 0   | RTS = 1, pas d'interruption en transmission                 |

| 1   | 1   | RTS = 0, envoi de break, pas d'interruption en transmission |

Contrôle des interruptions en réception CR 7

- CR 7 = 1, la ligne INT passe au niveau bas lorsque le registre de réception est plein ou si un "Overrun" intervient.

Registre d'état (SR) RS = 0 et R/W = 1

- bit 0 (Reception Data Register Full) à "1" indique que le registre de réception est plein. Le bit 0 est remis à "0" après une lecture du registre de réception.

- bit 1 (Transmission Data Register Empty) à "1" indique que le registre de transmission est vide, une nouvelle donnée peut être envoyée.

- bit 2 (Data Carrier Detect) à "1" indique une perte de la porteuse de données.

- bit 3 (Clear To Send) reflète l'état de l'entrée CTS.

- bit 4 (Framing Error) à "1" indique une erreur de format.

- bit 5 (Over Run) à "1" indique une surcharge : plusieurs caractères ont été reçus avant la lecture du précédent.

- bit 6 (Parity Error) à "1" indique une erreur de parité.

- bit 7 (Interrupt Request) à "1" une interruption a été positionnée.

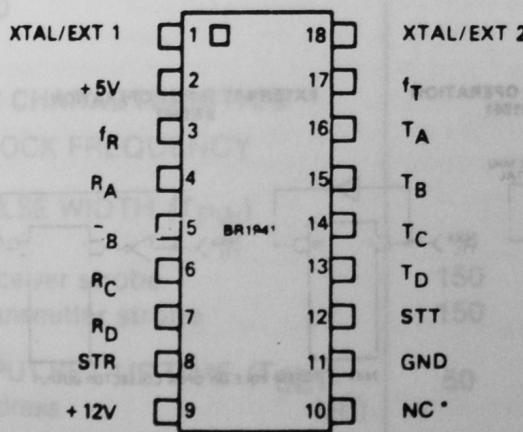

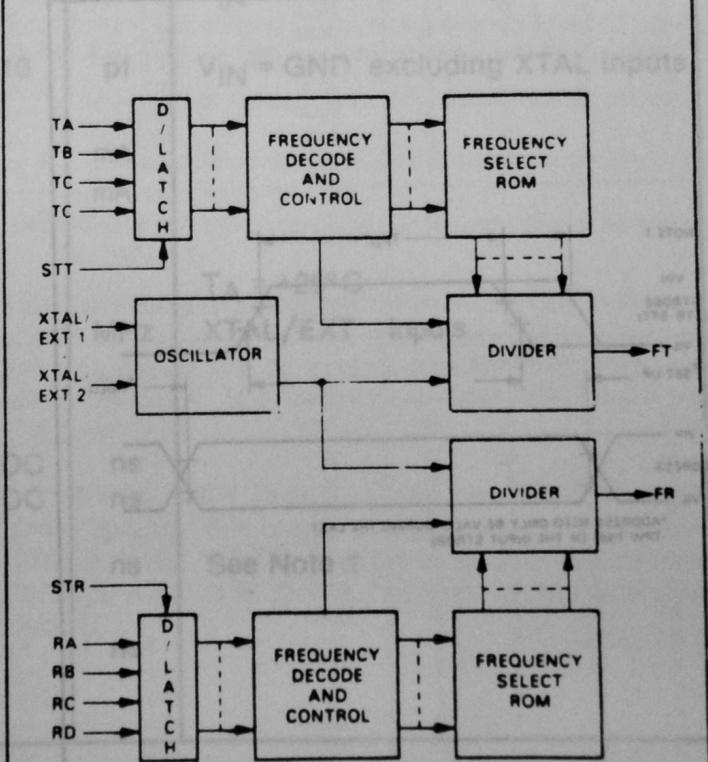

#### B) Le BRG 1941

Le BRG 1941 est un générateur de bauds qui fournit les horloges de transmission et de réception des 2 ACIAS. Le block diagramme de ce circuits est donné en figure 8. Ce circuits possède 2 voies indépendantes. La programmation de ces voies se fait par le bus de données : les 4 bits de poids faibles déterminent la fréquence de l'horloge sur la sortie **FR** ; les 4 bits de poids forts permettent de programmer la fréquence de la sortie **FT**. Le tableau suivant indique la correspondance.

| FR (bauds) | D0-D3 | FR (bauds) | D4-D7 |

|------------|-------|------------|-------|

| 50         | 0     | 50         | 1     |

| 75         | 1     | 75         | 1     |

| 110        | 2     | 110        | 2     |

| 134,5      | 3     | 134,5      | 3     |

| 150        | 4     | 150        | 4     |

| 300        | 5     | 300        | 5     |

| 600        | 6     | 600        | 6     |

| 1200       | 7     | 1200       | 7     |

| 1800       | 8     | 1800       | 8     |

| 2000       | 9     | 2000       | 9     |

| 2400       | A     | 2400       | A     |

| 3600       | B     | 3600       | B     |

| 4800       | C     | 4800       | C     |

| 7200       | D     | 7200       | D     |

| 9600       | E     | 9600       | E     |

| 19200      | F     | 19200      | F     |

La validation de la donnée est effectuée par les signaux STR et STT, générés pour les adresses FF003 et FF006. L'ACIA 68B50 non utilisée par le clavier est adressée en FF000 (commande et état) et FF001 (réception et transmission). L'ACIA utilisée par le clavier est adressée en FF004 et FF005?

FF000 } ACIA 1

FF001 }

FF002, horloge ACIA 1

FF004 } ACIA 2

FF005 }

FF006 horloge ACIA 2

## VI- L'éeprom moniteur

Sur cette version 1 de la carte CPU l'EPROM Moniteur est une 2732 A et à donc une capacité de 4 Koctets.

A l'initialisation du système le 68B09 positionne sur le bus l'adresse FFFE ce qui génère le signal FFXX à la sortie de 5B (74F30). Ce signal est utilisé pour forcer le décodage de la prom par le pal 4C lorsque la ligne R/W est à 1 (lecture). De même lorsque l'adresse FEXXX est décodée par 2C (74F30) et que A12 est à 1 la prom est validée. En résumé la prom 2732 est décodée de FF7FF à FFFF en lecture.

## VII- Circuits divers

### A) L'horloge

Elle est constituée de 7B (74S04) câblé en oscillateur piloté par un quartz à 8 MHz. Ce signal est appliqué à l'entrée Extal du 68B09 qui le divise par 4 afin de générer Q et E.

### B) Le Reset

L'impulsion de Reset est mise en forme par 2H (1/2 556). La donnée de l'impulsion, déterminée par la constante de temps R20.C16 est de 100 ms. A la mise sous tension une impulsion de 100 ms est également générée du fait de la constante de temps R23.C19. L'interrupteur Reset est fixé à l'arrière de la carte.

### C) Le NMI (Abort)

Le NMI (Interruption Non Masquable) permet de reprendre le contrôle, lors d'une boucle par exemple. L'impulsion de NMI est également générée par 2H (1/2 556). L'activation de ce signal se fait par un bouton-poussoir fixé sur la partie gauche de la console et relié à la carte.

Lors d'une NMI, le contrôle est donné au moniteur après affichage de tous les registres.

### D) Le mode DMA

Lors de la demande d'un accès DMA, les lignes Halt ou Brq sont activées. Les bascules 7A (74LS74) synchronise les demandes DMA avec E pour BRQ et Q pour Halt. En réponse le 68B09 active sa ligne BA (Bus Available) ce qui invalide les buffers 1B, 2A, 1C (bus d'adresse) et 6C (R/W). Le signal BA, amplifié par 6A (74LS244) est disponible sur le bus.

+ LE GENERATEUR DE BAUDS +

# BR1941 Dual Baud Rate Clock

## FEATURES

- 16 SELECTABLE BAUD RATE CLOCK FREQUENCIES

- DUAL SELECTABLE 16 X CLOCK OUTPUTS FOR FULL DUPLEX OPERATIONS

- OPERATES WITH CRYSTAL OSCILLATOR OR EXTERNALLY GENERATED FREQUENCY INPUT

- ROM MASKABLE FOR NON-STANDARD FREQUENCY SELECTIONS

- INTERFACES EASILY WITH MICRO-COMPUTERS

- OUTPUTS A 50% DUTY CYCLE CLOCK WITH 0.01% ACCURACY

- 18 PIN CERAMIC DIP PACKAGE

- 3 DIFFERENT FREQUENCY/DIVISOR PAIRS AVAILABLE

## GENERAL DESCRIPTION

The BR1941 is a combination Baud Rate Clock Generator and Programmable Divider. It is manufactured in N-channel MOS using silicon gate technology. This device is capable of generating 16 externally selected clock rates whose frequency is determined by either a single crystal or an externally generated input clock. The BR1941 is a programmable counter capable of generating a division from 2 to  $(2^{15} - 1)$ .

The BR1941 is available programmed with the most used frequencies in data communication. Each frequency is selectable by strobing or hard wiring each of the two sets of four Rate Select inputs. Other frequencies/division rates can be generated by reprogramming the internal ROM coding through a MOS mask change. Additionally, further clock division may be accomplished through cascading of devices. The frequency output is fed into the XTAL/EXT input on a subsequent device.

The BR1941 can be driven by an external crystal or by TTL logic.

\*INTERNALLY BONDED. DO NOT CONNECT ANYTHING TO THIS PIN.

## PIN CONNECTIONS

## BR1941 BLOCK DIAGRAM

**MOTOROLA****66,536-BIT DYNAMIC RAM**

The MCM6665 is a 66,536 bit, high speed, dynamic Random-Access Memory. Organized as 66,536 one-bit words and fabricated using NMOS high-performance N-channel silicon-gate technology. This new breed of 5-volt only dynamic RAM combines high performance with low cost and improved reliability.

By multiplexing row- and column-address inputs, the MCM6665 requires only eight address lines and permits packaging in standard 16-pin dual-in-line packages. Complete address decoding is done on chip with address latches incorporated. Data out is controlled by CAS allowing for greater system flexibility.

All inputs and outputs, including clocks, are fully TTL compatible. The MCM6665 incorporates a one-transistor cell design and dynamic storage techniques.

- Organized as 66,536 Words of 1 Bit

- Single +5 V Operation

- Fast 150 ns Operation

- Low Power Dissipation

- 275 mW Maximum (Active)

- 30 mW Maximum (Standby)

- Three-State Data Output

- Internal Latches for Address and Data Input

- Early-Write Common I/O Capability

- 16K Compatible 128-Cycle, 2 ms Refresh

- RAS-only Refresh Mode

- CAS Controlled Output

- Upward Pin Compatible from the 16K RAM (MCM4116, MCM4517)

**BLOCK DIAGRAM****MCM6665****MOS**

(IN-CHANNEL, SILICON-GATE)

**66,536-BIT

DYNAMIC RANDOM ACCESS

MEMORY****L SUFFIX

CERAMIC PACKAGE

CASE 880****PIN ASSIGNMENT**

|     |   |    |       |

|-----|---|----|-------|

| N/C | 1 | 16 | VSS   |

| D   | 2 | 15 | CAS   |

| W   | 3 | 14 | Q OUT |

| RAS | 4 | 13 | A6    |

| A0  | 5 | 12 | A3    |

| A2  | 6 | 11 | A4    |

| A1  | 7 | 10 | A5    |

| VCC | 8 | 9  | A7    |

\*For maximum compatibility with MCM6632 and MCM6664 a VCC trace should go to pin #1.

| <b>PIN NAMES</b> |                       |

|------------------|-----------------------|

| A0-A7            | Address Input         |

| D                | Data In               |

| Q                | Data Out              |

| W                | Read/Write Input      |

| RAS              | Row Address Strobe    |

| CAS              | Column Address Strobe |

| VCC              | Power (+5 V)          |

| VSS              | Ground                |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to the high-impedance circuit.

**MOTOROLA**

**Semiconductors**

## Advance Information

### 8-BIT MICROPROCESSING UNIT

The MC6809 is a revolutionary high performance 8-bit microprocessor which supports modern programming techniques such as position independence, reentrancy, and modular programming.

This third-generation addition to the MC6800 family has major architectural improvements which include additional registers, instructions and addressing modes.

The basic instructions of any computer are greatly enhanced by the presence of powerful addressing modes. The MC6809 has the most complete set of addressing modes available on any microprocessor today.

The MC6809 has hardware and software features which make it an ideal processor for higher level language execution or standard controller applications.

#### MC6800 COMPATIBLE

- Hardware - Interfaces with All M6800 Peripherals

- Software - Upward Source Code Compatible Instruction Set and Addressing Modes

#### ARCHITECTURAL FEATURES

- Two 16-bit Index Registers

- Two 16-bit Indexable Stack Pointers

- Two 8-bit Accumulators can be concatenated to form one 16-bit Accumulator

- Direct Page Register allows Direct Addressing throughout memory map

#### HARDWARE FEATURES

- On chip oscillator (4 X fo XTAL)

- DMA/BREQ allows DMA operation or memory refresh

- Fast Interrupt Request Input stacks only Condition Code Register and Program Counter

- MRDY Input extends data access times for use with slow memory

- Interrupt Acknowledge output allows vectoring by devices

- SYNC Acknowledge output allows for synchronization to external event.

- Single Bus-cycle RESET

- Single 5-volt operation

- NMI blocked after RESET until after first load of Stack Pointer

- Early address valid allows use with slower memories

#### SOFTWARE FEATURES

- 10 Addressing Modes

- 6800 Upward compatible Addressing Modes

- Direct Addressing anywhere in memory map

- Long Relative Branches

- Program Counter Relative

- Indirection

- Expanded Index Addressing

- 0.5,8,16-bit constant offsets

- 8, 16-bit accumulator offsets

- Auto-increment/decrement

- Improved Stack Manipulation

- 1464 Instructions with unique addressing modes

- 8 x 8 unsigned multiply

- 16-bit arithmetic

- Transfer/Exchange all registers

- Push/Pull any or all registers

- Load Effective Address

**MC6809**

(1.0 MHz)

**MC68A09**

(1.5 MHz)

**MC68B09**

(2.0 MHz)

**MOS**

(N-CHANNEL, SILICON-GATE)

### 8-BIT MICROPROCESSING UNIT

#### PIN ASSIGNMENT

|    |             |       |    |

|----|-------------|-------|----|

| 1  | VSS         | HALT  | 40 |

| 2  | NMI         | XTAL  | 39 |

| 3  | IRQ         | EXTAL | 38 |

| 4  | FIRQ        | RESET | 37 |

| 5  | BS          | MRDY  | 36 |

| 6  | BA          | 0     | 35 |

| 7  | VCC         | E     | 34 |

| 8  | A0 DMA/BREQ |       | 33 |

| 9  | A1          | R/W   | 32 |

| 10 | A2          | D0    | 31 |

| 11 | A3          | D1    | 30 |

| 12 | A4          | D2    | 29 |

| 13 | A5          | D3    | 28 |

| 14 | A6          | D4    | 27 |

| 15 | A7          | D5    | 26 |

| 16 | A8          | D6    | 25 |

| 17 | A9          | D7    | 24 |

| 18 | A10         | A15   | 23 |

| 19 | A11         | A14   | 22 |

| 20 | A12         | A13   | 21 |

**MOTOROLA****MCM6665****65,536-BIT DYNAMIC RAM**

The MCM6665 is a 65,536 bit, high-speed, dynamic Random-Access Memory. Organized as 65,536 one-bit words and fabricated using HMOS high-performance N-channel silicon-gate technology. This new breed of 5-volt only dynamic RAM combines high performance with low cost and improved reliability.

By multiplexing row- and column-address inputs, the MCM6665 requires only eight address lines and permits packaging in standard 16-pin dual-in-line packages. Complete address decoding is done on chip with address latches incorporated. Data out is controlled by CAS allowing for greater system flexibility.

All inputs and outputs, including clocks, are fully TTL compatible. The MCM6665 incorporates a one-transistor cell design and dynamic storage techniques.

- Organized as 65,536 Words of 1 Bit

- Single + 5 V Operation

- Fast 150 ns Operation

- Low Power Dissipation

275 mW Maximum (Active)

30 mW Maximum (Standby)

- Three-State Data Output

- Internal Latches for Address and Data Input

- Early-Write Common I/O Capability

- 16K Compatible 128-Cycle, 2 ms Refresh

- RAS-only Refresh Mode

- CAS Controlled Output

- Upward Pin Compatible from the 16K RAM (MCM4116, MCM4517)

**BLOCK DIAGRAM****MOS**

(IN-CHANNEL, SILICON-GATE)

**65,536-BIT

DYNAMIC RANDOM ACCESS

MEMORY**

L SUFFIX

CERAMIC PACKAGE

CASE 680

**PIN ASSIGNMENT**

|     |   |    |       |

|-----|---|----|-------|

| N/C | 1 | 16 | VSS   |

| IN  | 2 | 15 | CAS   |

| W   | 3 | 14 | Q OUT |

| RAS | 4 | 13 | A6    |

| A0  | 5 | 12 | A3    |

| A2  | 6 | 11 | A4    |

| A1  | 7 | 10 | A5    |

| VCC | 8 | 9  | A7    |

\*For maximum compatibility with MCM6632 and MCM6664 a VCC trace should go to pin #1.

**PIN NAMES**

|       |                       |

|-------|-----------------------|

| A0-A7 | Address Input         |

| D     | Data In               |

| Q     | Data Out              |

| W     | Read/Write Input      |

| RAS   | Row Address Strobe    |

| CAS   | Column Address Strobe |

| VCC   | Power (+ 5 V)         |

| VSS   | Ground                |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.